В наші дні осцилограф є доступним приладом для будь-якого майстра або любителя. З розвитком електроніки прості інструменти тестування, такі як логічні пробники, в наші дні не так популярні. Однак, якщо осцилограф або логічний аналізатор поза досяжністю, логічний пробник-зручний інструмент для перевірки цифрових схем.

Крім того, в деяких випадках логічний пробник є простим варіантом для перевірки працездатності низькошвидкісних логічних схем, оскільки він забезпечує візуальну індикацію логічного стану в реальному часі без коригувань або калібрувань.

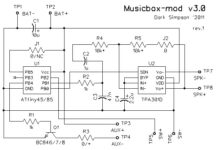

У конструкції логічного пробника, описаної в цій статті, використовуються поширені і недорогі інтегральні схеми, в тому числі популярний таймер ne555 і інтегральна схема компаратора низької напруги lm393.

Інструменти та матеріали:-smd – конденсатори 0805022mfd – 1 шт. 0.0022 mfd – 2 шт. 0,01 mfd – 2 шт.;-smd резистори 080520 ком – 2 шт. 100 ком – 1 шт. 18 ком – 1 шт. 5,1 ком – 1 шт. 15 ком – 1 шт. 30 ком – 1 шт. 4,7 мом – 1 шт. 330 ом – 2 шт. 5,6 ком – 2 шт. 12 ком – 1 шт. 470 ом – 1 шт.;-діод smd ll4148 – 2 шт;-діод smd m4 – 1 шт;-3-контактний міні-мікроперемикач 1p2t ss12d07 – 1 шт;-мікросхема lm393 (smd спк-8) – 1 шт;-мікросхема ne555 (smd спк-8) – 1 шт;-червоний світлодіод 3 мм – 1шт;-зелений світлодіод 3 мм – 1 шт;-жовтий світлодіод 3 мм – 1 шт;-паяльні приналежності;

Крок перший: друкована плата логічного пробникау цій платі використовуються компоненти smd для мінімізації розміру плати. Розміри розпаяної друкованої плати становлять близько 70 мм × 14 мм × 6,6 мм, а розмір корпусу, надрукованого на 3d-принтері, складає всього 90 мм × 26 мм × 14 мм. Файли проекту друкованої плати kicad, схеми, файли gerber і схема тестової установки цього проекту доступні за адресою https://drive.google.com/file/d/1locekmoqazpllfvxj9uzrg2j7vz-qiva/view ..logic-probe.pdf

Крок другий: пайка друкованої платидля складання цієї друкованої плати не потрібно спеціального паяльного обладнання. Як показано на відео, цю друковану плату можна зібрати за допомогою стандартного паяльника 30 – 40 вт.

Щуп майстер виготовив з мідного дроту. Кінець дроту потрібно загострити, а потім облудити зонд.

Крок четвертий: корпусдизайн корпусу для цього логічного пробника доступний на tinkercad. Верхня і нижня кришки корпусу друкуються на 3d-принтері. Матеріал для друку abs або pla.

Ця конструкція корпусу передбачає, що на друкованій платі встановлені світлодіоди 3 мм і наконечник пробника 12 swg (2,6 мм). Якщо компоненти відрізняються від зазначених розмірів, то може знадобитися відповідне коригування компонування корпусу.верхня і нижня частини корпусу збираються за допомогою клею.так само файли для друку можна завантажити нижче.top cover.stlbottom cover.stl

Схема використовувана для перевірки логіки зонда складається з таймера ne555, двухcd4040 (двійковий лічильник на 12 розрядів) і cd4017 (лічильник має 10 виходів). У цій схемі ne555 забезпечує вихідну частоту 16 кгц з робочим циклом приблизно 50%. Лічильники cd4040 використовуються в якості дільника частоти для генерації сигналів 500 гц і 15 гц.

Ця тестова схема може використовуватися для перевірки всіх станів логічного пробника .ця схема необхідна, якщо немає генератора частоти для перевірки працездатності логічного пробника.схема випробувальної установки додається у вигляді pdf-файлу.logic-probe-test.pdf

Цей пробник має три світлодіодних індикатора і відображає логічні рівні ( високий і низький рівень ) і імпульсні сигнали з частотою до 1,8 мгц (при робочому циклі 60%).

Для роботи цього логічного пробника потрібно підключити провід живлення логічного пробника до джерела постійного струму. Напруга живлення має бути від 3в до 15в.напруги вище цього діапазону можуть пошкодити іс логічного пробника.

Залежно від перевіряється схеми потрібно встановити перемикач в положення cmos або ttl і можна починати тестування, доторкнувшись наконечником пробника до компонентів друкованої плати. Для розшифровки вихідного сигналу дивимося додається таблицю.

Індикатор імпульсів (червоний світлодіод) чутливий до імпульсних сигналів з більш високою частотою в діапазоні від 13 кгц до 200 кгц із середнім робочим циклом 50%. Максимальна частота, підтримувана цим логічним пробником, становить 1,8 мгц при робочому циклі 60%.

джерело (source)